linux

python

ui

excel

节日

寒武纪面试

硬件设备

Nanoprobes

控制算法

增强现实

webrtc

软件测试工程师

数据压缩

如何修复网站漏洞

startup packet

端口转发

字节打印流

测试员

SecOC

validation

cadence

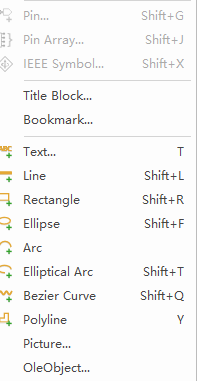

2024/4/11 18:30:54Cadence OrCAD Capture绘制多边形实例——Polyline

Cadence OrCAD Capture绘制多边形实例——Polyline代码执行结果代码

proc fiveStar {len} {set x0 3.0set y0 3.0#set len 2.0set pi 3.141592654set x1 [expr $x0 $len*cos(36*$pi/180)]set y1 [expr $y0 - $len*sin(36*$pi/180)]PlacePolyline $x0 $y0 $x1 $y1set x2 [expr…

Cadence OrCAD Capture TCL/TK脚本实例

Cadence OrCAD Capture TCL/TK脚本实例获取当前Session创建新的Session获取Session的设计遍历Session中所有的设计获取设计中的原理图遍历设计中的所有原理图获取原理图中的页遍历原理图中所有页遍历原理图页中所有元件实例遍历原理图页中所有的wire遍历原理图页中的所有全局变…

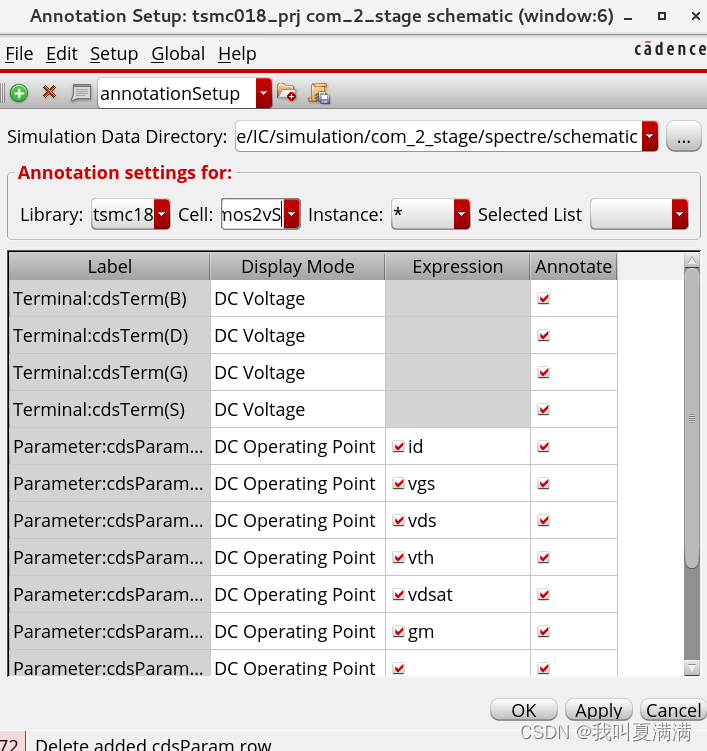

cadence DC仿真后如何查看每个管子的参数

一、 选DC Operating point,选mos管 二、 选result browser,找dc里面的

Cadence改背景色

白色转成黑色背景:

打开终端命令窗口后,输入

echo "Opus.editorBackground: white" | xrdb -merge 黑色转换成白色背景: 打开终端命令窗口后,输入 echo "Opus.editorBackground: black" | xrdb -merge

*Error* No simulation output data has been selected.(cadence仿真)

要先设置直流状态仿真一遍 然后就可以获取calculator中的list值

Cadence报错ERROR: Netlister: can‘t find the date RFIC_sim/gmid/schematic was last extra

ERROR: Netlister: cant find the date RFIC_sim/gmid/schematic was last extra 运行先一定要check & save(x)

改变cadence的字体大小

CIW中打入

hiSetFont("ciw" ?size 16)

hiSetFont("label" ?name "Open Sans" ?size 16)

hiSetFont("text" ?name "Open Sans" ?size 16)

Cadence Allegro 导出Symbol Pin Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Symbol Pin Report作用3,Symbol Pin Report示例4,Symbol Pin Report导出方法4.1,方法14.2,方法2B站关注“硬小二”浏览更多演示视频 1,概述 本文简单

Cadence Allegro 导出Net Single Pin and No Pin报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Net Single Pin and No Pin作用3,Net Single Pin and No Pin示例4,Net Single Pin and No Pin导出方法4.1,方法14.2,方法2B站关注“硬小二”浏览更多演示视频

快速掌握Allegro PCB内电层铺铜设计专题

🏡《总目录》 🏡《宝典目录》 目录 1,概述2,大纲Cadence Allegro 铺铜及内电层设计方法Cadence Allegro 为铜皮分配网络Cadence Allegro 关闭或打开铜皮显示Cadence Allegro 动态铜皮不避让走线解决方案Cadence Allegro 修改静态铜皮为动态铜皮Cadence Allegro 修改编…

Cadence Allegro 导出Etch Length by Net Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Etch Length by Net Report作用3,Etch Length by Net Report示例4,Etch Length by Net Report导出方法4.1,方法14.2,方法2B站关注“硬小二”浏览更多演示视频

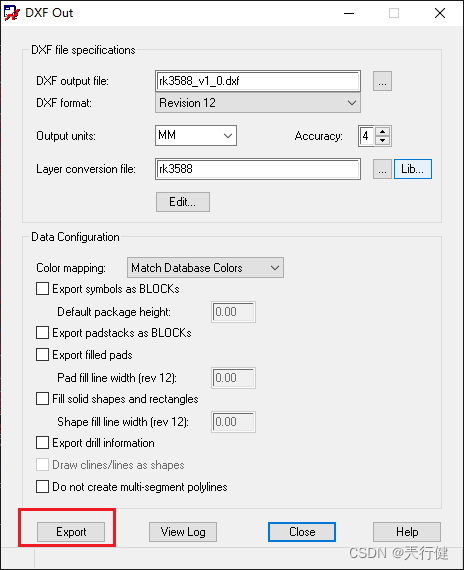

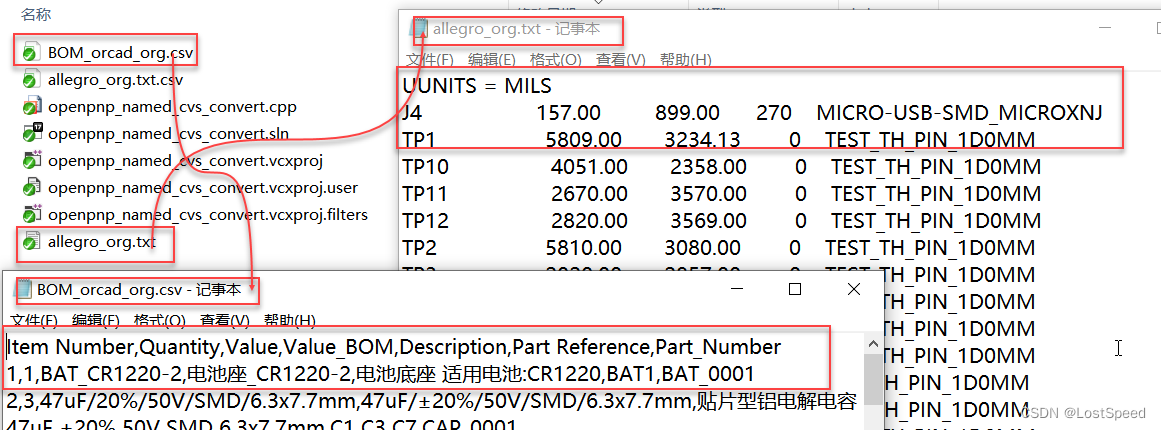

cadence SPB17.4 - export placement file to openpnp

文章目录cadence SPB17.4 - export placement file to openpnp概述笔记openpnp支持的坐标文件格式openpnp导入坐标文件的内容规则制作openpnp可用的坐标文件的思路列表先自己写个程序试试, 这个不难, 也省心程序写完了,好使转换前的allego原版坐标文件转换后的openp…

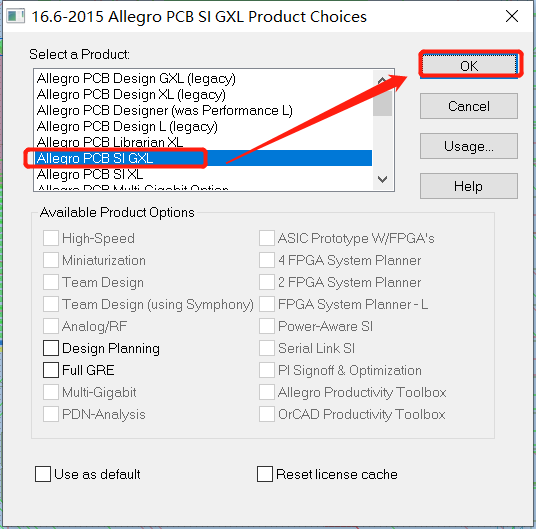

Cadence PCB仿真 使用Allegro PCB SI为BRD文件创建通用型IBIS模型的方法图文教程

⏪《上一篇》 🏡《总目录》 ⏩《下一篇》 1,概述 本文简单介绍使用Allegro PCB SI软件为BRD PCB设计文件中的元器件创建IBIS模型的方法。 2,创建方法

第1步:确定打开PCB文件的软件是 Allegro PCB SI 如果不是Allegro PCB SI,可执行File→Change Editor…更换软…

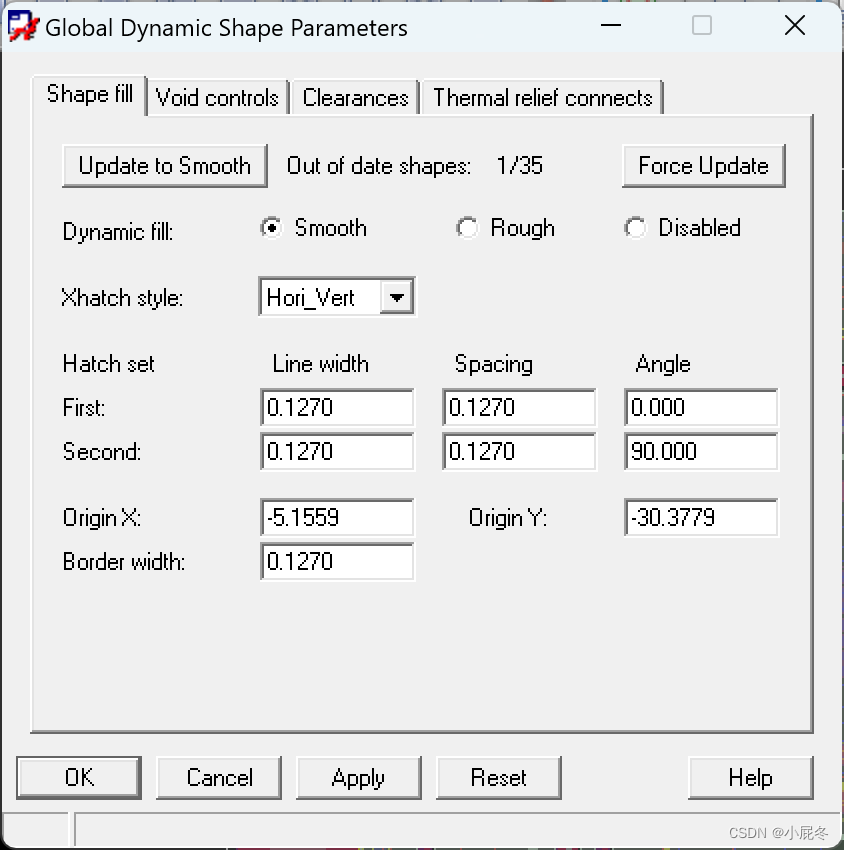

ALLEGRO之SHAPE

ALLEGRO中的SHAPE菜单对应AD中的Polygon Pour,即铺铜操作。 1. Polygon:铺铜,在Options选择对应子层(例如Etch-Top),选择Dynamic copper(动态铺铜,会自动避让过孔,Static…

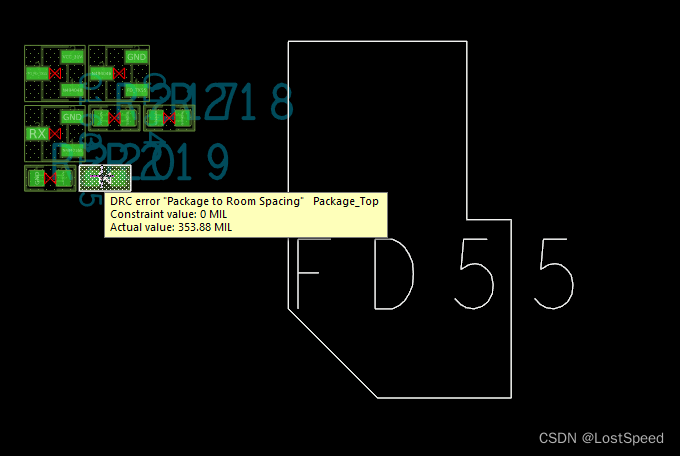

cadence SPB17.4 S032 - 使用room来放置元件

文章目录 cadence SPB17.4 S032 - 使用room来放置元件概述笔记在orcad中设置子原理图的ROOM号码在空的Allegro工程中, 放入板框在allegro中建立room备注补充 - ROOM还得留着END cadence SPB17.4 S032 - 使用room来放置元件

概述

如果在allegro中直接手工或自动放置元件, 放好…

Cadence网表文件解析

Cadence网表文件解析概述注释How properties are netlisted from Capture to PCB EditorPCB编辑器Netlist文件PSTCHIP.DATPSTCHIP文件格式PSTCHIP文件元素PSTCHIP样例PSTXNET.DATPSTXNET.DAT的组成元素PSTXNET样例PSTXPRT.DATPSTXPRT.DAT文件元素PSTXPRT.DAT文件格式PSTXPRT.DA…

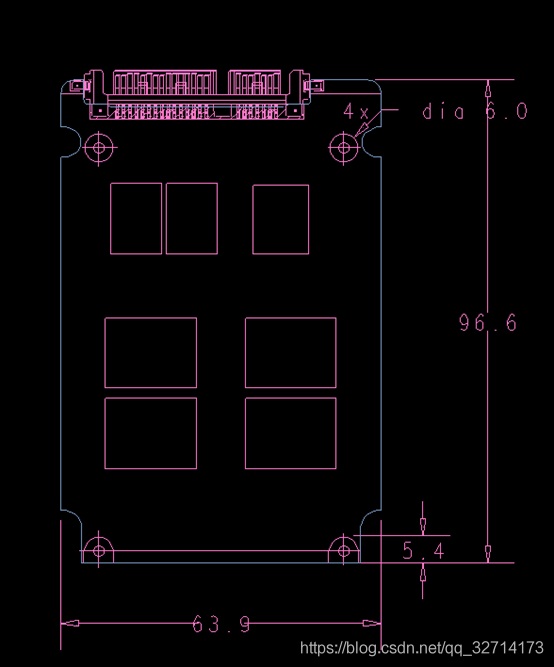

Cadence PCB 焊盘和封装

封装(Packaging)

封装指的是在电子元件制造中将电子元件(例如集成电路芯片、电子元器件等)进行物理保护和连接的过程。封装通常涉及将电子元件封装到外部保护壳或包装中,以确保其正常运作、连接到电路板并保护它们免受环境因素的影响。

封装的主要目标包括以下几个方面:…

快速掌握Allegro PCB设计检查专题

🏡《总目录》 🏡《宝典目录》 目录 1,概述2,大纲Cadence Allegro 忽略DRC标识方法Cadence Allegro 恢复忽略的DRC标识的方法Cadence Allegro 修改DRC标识大小Cadence Allegro 修改DRC标识颜色Cadence Allegro 修改Waived DRC标…

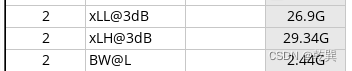

【Cadence】Calculator计算sp的3dB带宽

【Cadence】Calculator计算sp的3dB带宽 1.计算最大增益2.cross函数3. 3dB带宽 下面演示如何在Cadence计算s参数(如增益)的3dB带宽 1.计算最大增益

ymax函数

2.cross函数

cross函数可以计算经过y轴给定值对应的x坐标 edge number选择1是经过的第一个点…

C6—Cadence导出的csv转成xdc文件20230902

Vivado工程需要引脚之间的连接才能生成bit流。使用cadence软件设计的原理图可以导出csv文件或者ucf文件,而使用vivado使用以xdc为后缀的文件。使用python读入csv文件,按照一定的格式转换成xdc文件保存,省去了手动添加的步骤。当然需要注意&am…

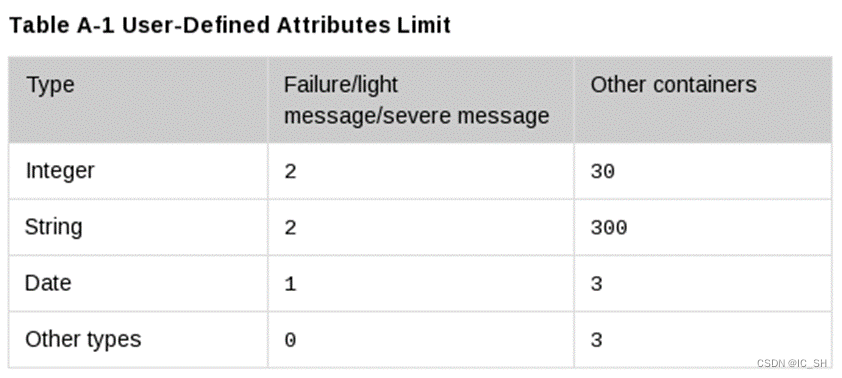

Cadence Vmanager vsif文件编写指南(持续更新...)

目录 1.NTF格式介绍

1.1.1 {属性:值}定义

1.1.2类别

1.1.3语法

2.vsif文件中有效的container

2.1 session {…} 1.NTF格式介绍

Cadence的Vmanager工具采用vsif类型的文件作为regression的输入文件,采用vplanx/csv类型的文件作为vplan的输入文件&am…

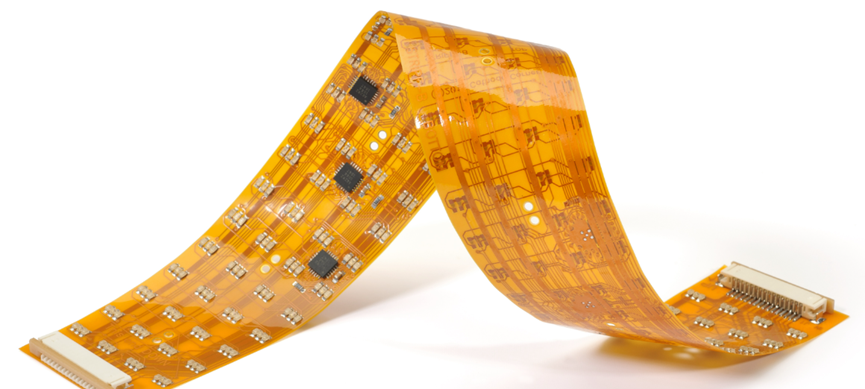

FPC柔性电路板介绍及PCB设计经验规则总结

🏡《总目录》 目录 1,概述2,FPC的特点3,FPC设计十五条经验规则4,总结1,概述 FPC软板由于具有可弯曲折叠的特点,当前在消费电子,汽车电子和航空航天领域应用广泛。本文详细介绍FPC的特点并对FPC板设计中需要注意的经验原则进行总结。 2,FPC的特点 FPC的全称是Flexibl…

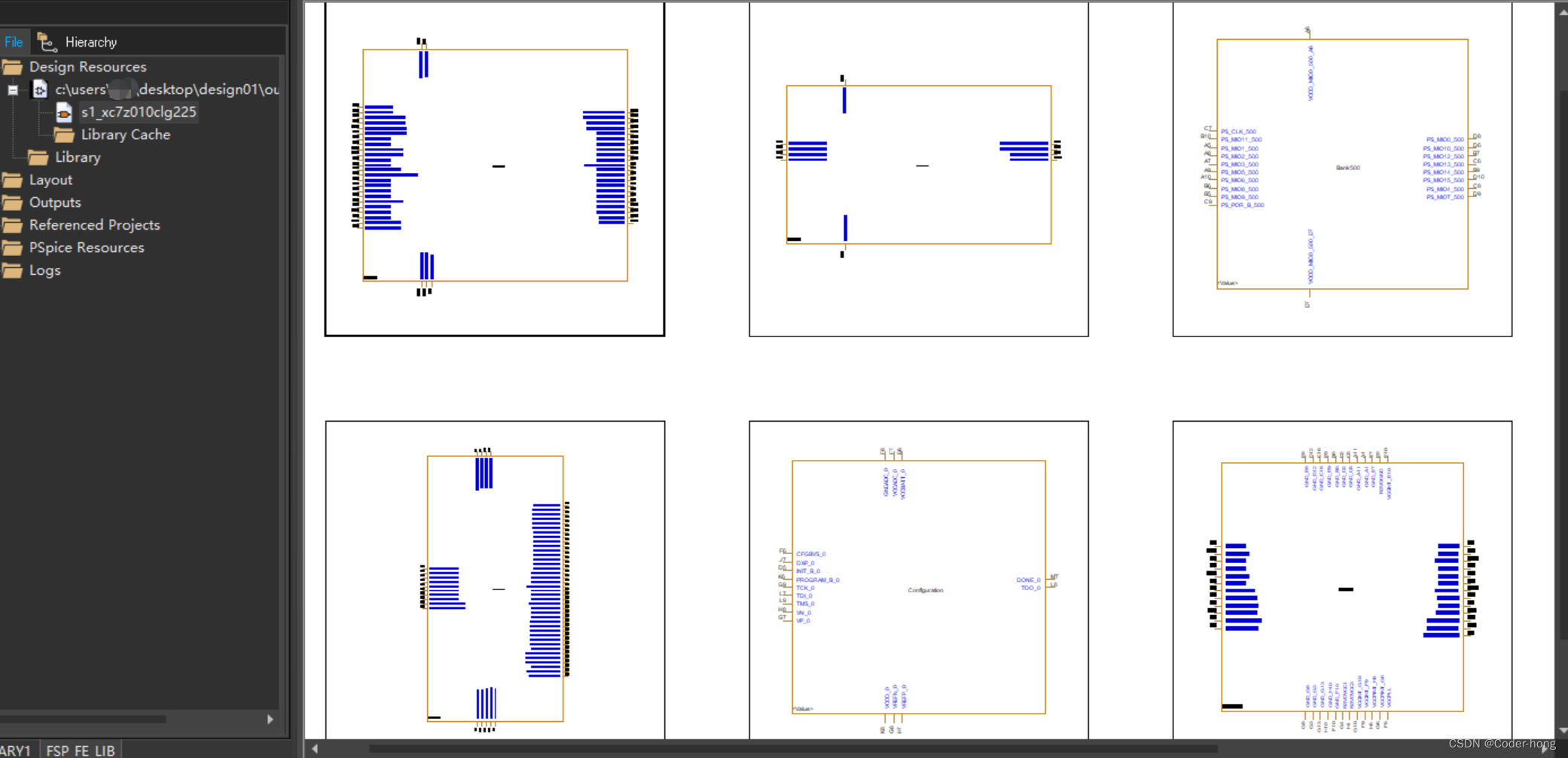

OrCAD创建原理图库

OrCAD创建原理图库 概述常规器件建库方法大封装器件建库基于pinout表格创建原理图库导入方法: 通过fsp软件导入fpga原理图库 概述

原理图库是硬件设计的基本工作,每个新人都要先学会建库,才能开始画图,本文主要介绍几种常用的建库…

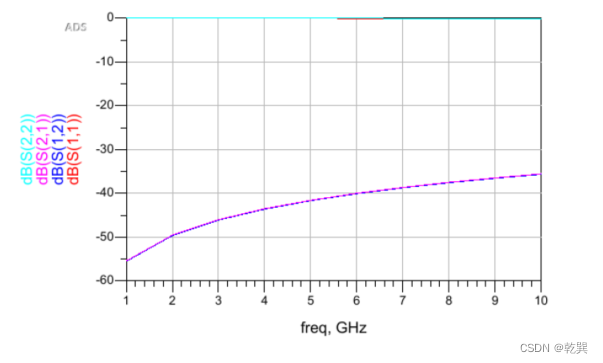

【Cadence】 ADS Dynamic Link使用教程

ADS Dynamic Link使用教程1.新建一个Cadence Schematic2.打开ADS3.在ADS新建Schematic4.加入控件OPTIONS5.加入Netlist6.仿真测试7.写在最后1.新建一个Cadence Schematic

随便搭了一个Cascode 注意这个时候不要新建symbol

2.打开ADS 3.在ADS新建Schematic

选择对应的Cadenc…

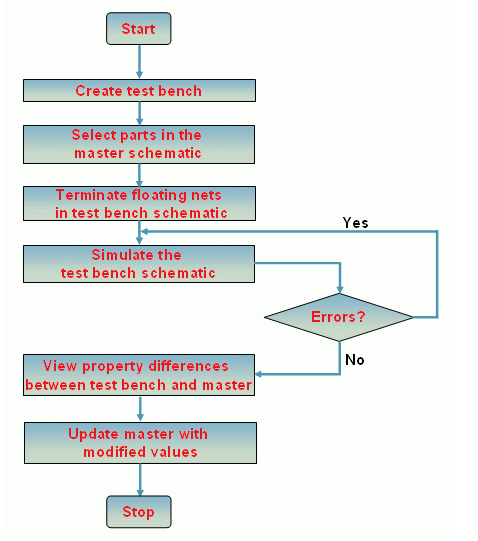

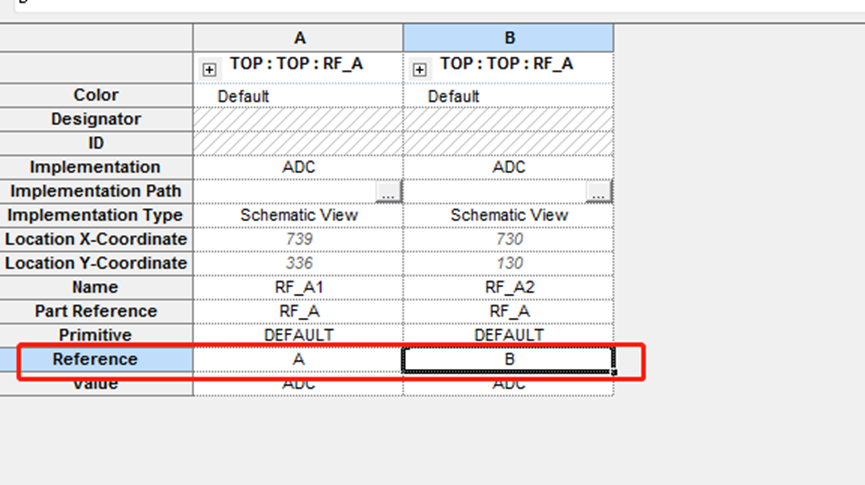

OrCAD原理图检查

OrCAD原理图检查 FPGA或处理器芯片原理图封装检查OrCad元件Part Reference与Reference位号不同检查所有器件是否与CIS库元件匹配用CIS库中的元器件替换已存在器件方法1方法2 DRC检查修改页码Annotate重排位号利用Intersheet References功能进行off-page索引检查封装、厂家、型号…

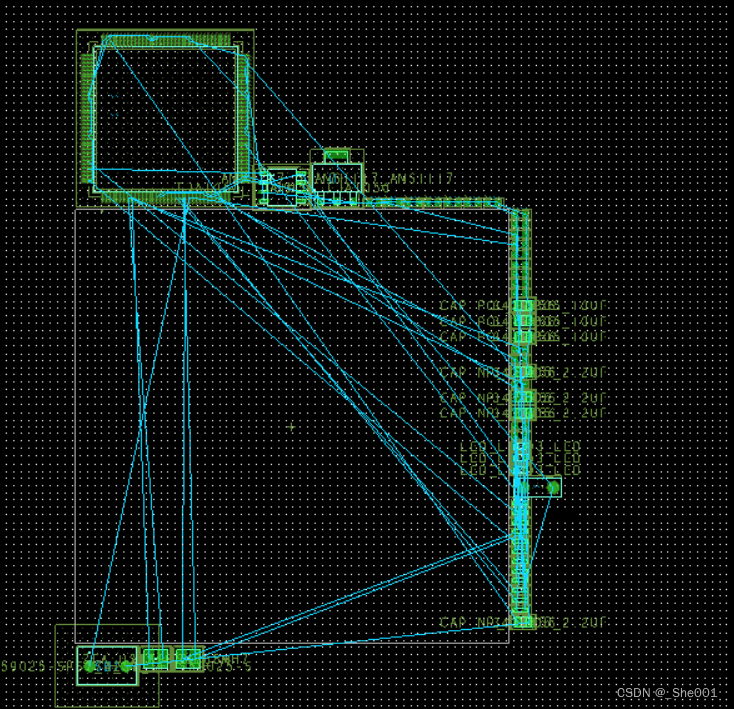

分享 | 使用Virtuoso VCPVSR工具基于标准单元的布局布线流程

本节内容 导览 一、准备工作 二、运行VCP前的配置 三、VCP的布局规划 四、VCP的自动摆放 五、VSR的自动绕线 分享使用Virtuoso GXL Custom Digital Placer(VCP) & Space-based Router(VSR)工具进行基于纯数字Standard-Cell布局布线的操作流程。 VCP&VSR演…

2小时掌握Allegro PCB 布局专题

🏡《总目录》 🏡《宝典目录》 目录 1,概述2,大纲Cadence Allegro 通孔PAD制作方法Cadence Allegro 摆放关键元件关键模块方法Cadence Allegro 对齐元件交换元件方法Cadence Allegro 等距离对齐元件方法Cadence Allegro 板框内缩创建布线区域和放置元件区域方法Cadenc…

Cadence OrCAD Capture CIS ODBC数据库文件在两台电脑上同步使用时一台电脑启动失败的问题解决图文教程

⏪《上一篇》 🏡《总目录》 ⏩《下一篇》 目录 1,问题概述2,问题原因3,解决方法3.1,电脑1配置方法:3.2,电脑的配置方法4,总结B站关注“硬小二”浏览更多演示视频 1,问题概述

执行Place→Database Part放置CIS库文

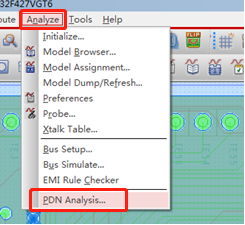

Cadence PCB仿真 使用 Allegro PCB SI 元器件端口设置的PDN分析功能介绍图文教程

🏡《总目录》 🏡《分目录》 目录 1,概述2,启动方法3,功能介绍3.1,元器件设置列表(Device)3.2,端口设置列表(Ports)4,总结1,概述 在进行PDN分析时需要对电源网络涉及到的所有元器件的指定端口的参数进行配置。本文介绍PDN网络元器件端口设置的功能。 2,启动…

Cadence Allegro 导出Film Area Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Film Area Report作用3,Film Area Report示例4,Film Area Report导出方法4.1,方法14.2,方法2B站关注“硬小二”浏览更多演示视频 1,概述 本文简单介绍什么是F

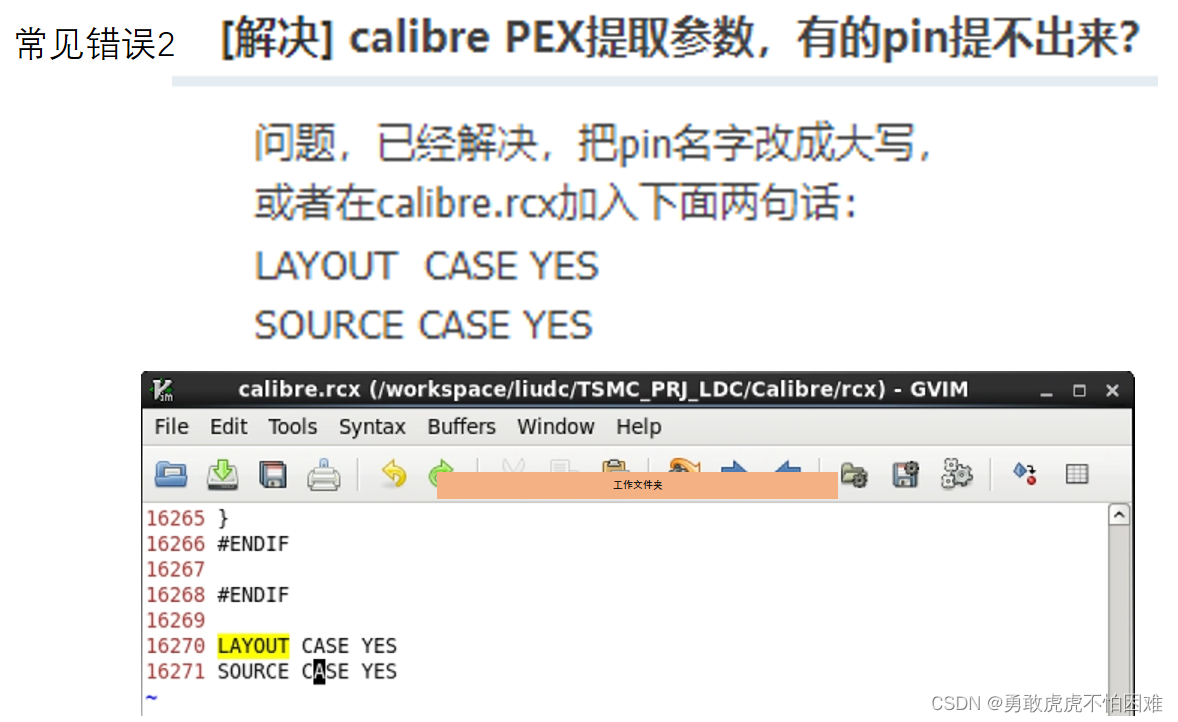

cadence后仿真/寄生参数提取/解决pin口提取不全的问题

post-simulation设置顺序与规则

1.Rules 设置

2.inputs设置 3.outputs设置 4.PEX 设置

会出现错误1,后有解决方案 第一步 :Netlist 第二步:LVS 5.RUN PEX

先RUN,后按照图中1 2 3步骤操作 点击OK之后,显示Calibre信息ÿ…

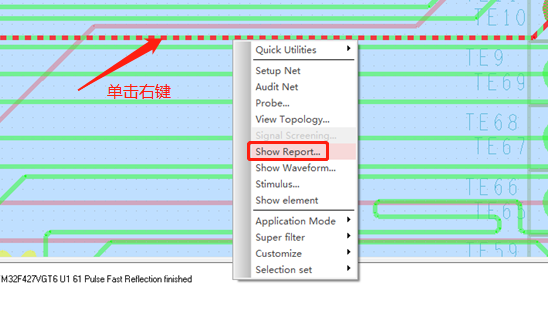

Cadence PCB仿真使用Allegro PCB SI生成反射仿真报告及报告导读图文教程

🏡《Cadence 开发合集目录》 🏡《Cadence PCB 仿真宝典目录》 目录 1,概述2,生成报告3,报告导读4,总结1,概述 本文简单介绍使用Allegro PCB SI生成网络的反射性能评估的报告的方法,及反射报告要点导读。 2,生成报告

第1步,选择需要生成报告的网络,然后单击右…

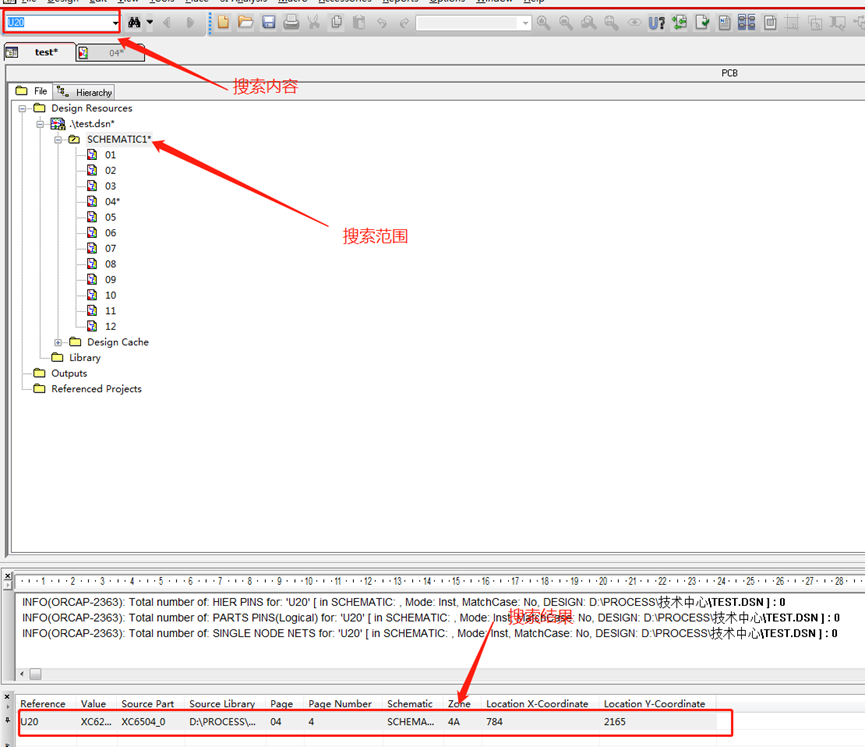

Cadence OrCAD Capture 搜索的到的元器件无法在图纸中找到的问题

🏡《总目录》 目录 1,概述2,问题现象3,问题原因解决方案4,总结B站关注“硬小二”浏览更多演示视频 1,概述 本文简单介绍在使用Capture绘图时,搜索元器件或其他对象,存在搜索结果,但在图纸中无法找到的原因和解决方案。 2,问题现象 如下图所示搜索U20后,存在搜索结果…

Allegro约束规则设计

首先是物理规则。 然后是间距规则。 如果有些特殊要求,还需要设计电气规则。

原则上,把规则设计好,然后把规则赋值给网络。 物理规则。PCS。

对于名字为DEFAULT的PCS,这是最基础的整板默认规则。 没有特殊要求的网络,…

[原创]Cadence17.4,win64系统,构建CIS库

目录 1、背景介绍 2、具体操作流程 3、遇到问题、分析鉴别问题、解决问题 4、借鉴链接并评论 1、背景介绍 CIS库,绘制原理图很方便,但是需要在Cadence软件与数据库之间建立联系,但是一直不成功,花费半天时间才搞明白如何建立关系并…

经验:OrCAD Capture卡顿问题的解决方法

经验:OrCAD Capture卡顿问题的解决方法 更新历史 20190612: 首次发布 Cadence软件是一款十分优秀的电路设计软件。然而,最近重新安装该软件(注:本人在Windows 10系统中安装的该软件)后却发现:

打开OrCAD Capture需要好…

cadence一些快捷键

2022/4/10 我感觉这是被人修改过了,应该用shifte 改快捷键的方法如何在Cadence Virtuoso中自定义快捷键?_Clara_D的博客-CSDN博客_virtuoso快捷键设置bindkey x 打开descend,进入模块内部 上箭头退出模块

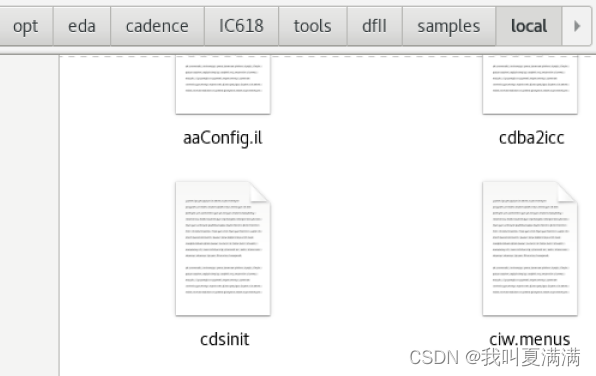

CentOS7安装Cadence IC617+MMSIM151+Calibre2015教程

CentOS7安装Cadence IC617MMSIM151Calibre2015教程 - 知乎一、安装前介绍Cadence 官网的平台有很多,根据自己的需要选择合适的平台,本文介绍其中的 Cstom IC / Analog/ RF Design (RF IC 设计)安装及其相关设置。安装的组件有&…

Cadence Allegro 导出Waived Design Rules Check Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Waived Design Rules Check Report作用3,Waived Design Rules Check Report示例4,Waived Design Rules Check Report导出方法4.1,方法14.2,方法2B站关注“硬小二”浏览更多演示视频

Cadence Allegro 导出Unplaced Component Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Unplaced Component Report作用3,Unplaced Component Report示例4,Unplaced Component Report导出方法4.1,方法14.2,方法2B站关注“硬小二”浏览更多演示视频

Allergo导出Gerber文件

首先设置导出路径,点击 Setup->User Preferences,在弹出的对话框中设置ads_sdart的值为Gerber(名字随意),该文件夹在当前.brd文件所在文件夹下。 一.板信息完善

1.设置孔径公差

1.选择 Manufacture->NC->Drill Customization&…

Allegro模块化布局常用技巧(group)

利用group功能,可以方便的进行快速的布局调整。

在placement模式下, 通常,是在板框外,将某个单元模块的电路,进行模块内布局后, 再框选为一个temp group, 或者手工进行temp group创建ÿ…

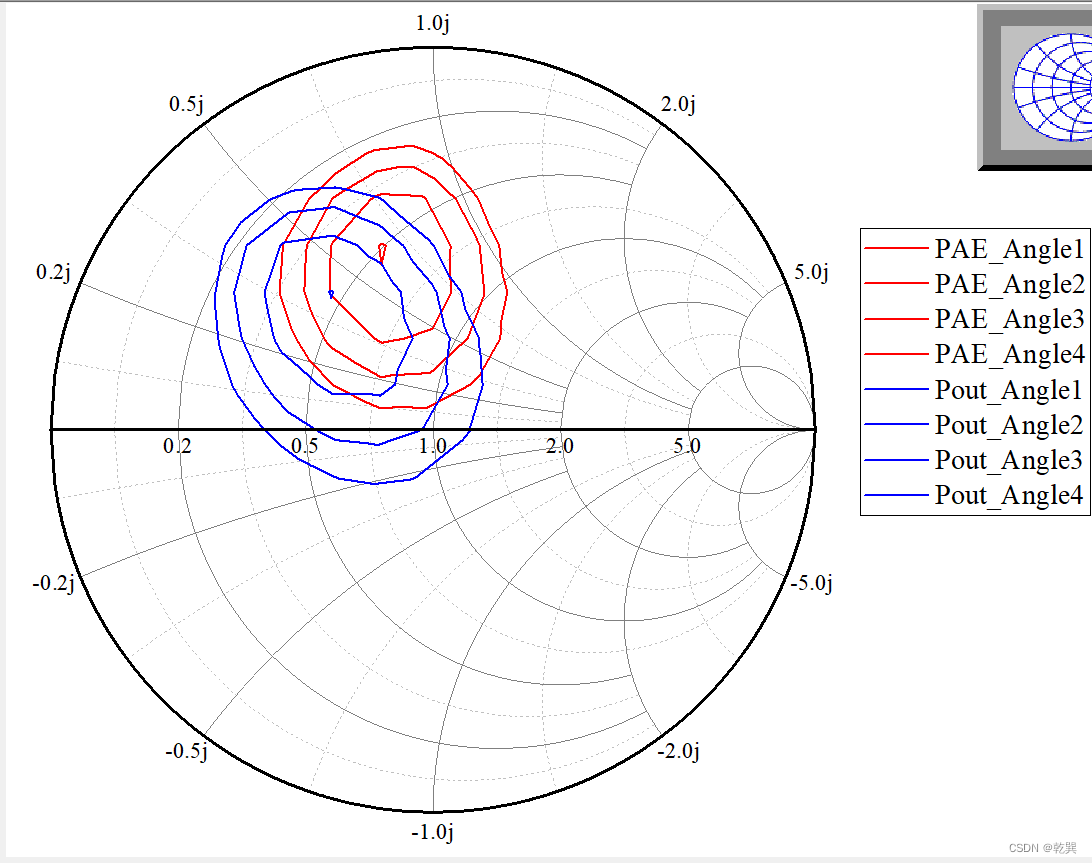

【origin】负载牵引的Smith圆图

【origin】负载牵引的Smith圆图 1.从ADS导入数据到origin2.smith圆图3.扩展到多组线4.参考资料 1.从ADS导入数据到origin export导出为txt,得到的是幅相值,复制到excel如下图,有多根类似格式的线,只需要复制DE列到origin中 复制到…

Cadence Allegro 导出Padstack Definition Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Padstack Definition Report作用3,Padstack Definition Report示例4,Padstack Definition Report导出方法4.1,方法14.2,方法2B站关注“硬小二”浏览更多演示视频

关闭Cadence startpage 页面的方法

17.2版本上述命令不起作用,删除安装路径中的tcl文件即可。 文件及路径:/Cadence/SPB_17.2/tools/capture/tclscripts/capAutoLoad/capStartPage.tcl

pads_in.log‘ does not exist.

pads_in.log does not exist. ALLEGRO 中导入PADS的asc文件时显示pads_in.log does not exit_Anitawen的博客-CSDN博客_allegro导入asc文件 Pads ASCII file containing illegal characters in padstack, decals which are not supported by Allegro, fail to execute in pads_…

cadence SPB17.4 S032 - Update Symbols失败的问题

文章目录 cadence SPB17.4 S032 - Update Symbols失败的问题概述笔记END cadence SPB17.4 S032 - Update Symbols失败的问题

概述

铺铜后, 进行DRC, 发现安装孔不太合适, 有DRC警告. 安装孔是一大孔, 上面打了一圈小孔. 这些小孔有警告, 说孔和孔之间不能干涉. 开始将这些DRC…

Cadence初次使用

SN n性注入层 AA 有源层 GT 栅极 M1 金属1 CT 连接有源和金属1层 NW n井层 SP p型注入层 shiftz 缩小 ctrlz 放大 shiftf 显示器件结构 ctrlf 隐藏器件结构 f全部显示 g 改随机格点 p 连线 r 画矩阵 k 测量工具 shiftk 取消尺子 c 复制 复制时按住鼠标右键旋转 …

Cadence 简易使用教程

原理图的快捷键

快捷键功能快捷键功能快捷键功能i添加元件l添加线名x保存并检查c复制w添加连线S(shift s)保存m移动W(shift w)添加粗线u取消上一步M(shiftm)移动(断线)n添加注释U(shiftu)恢复上一步del删除[缩小e进入下一层p添加pin]放大Ctrl &#…

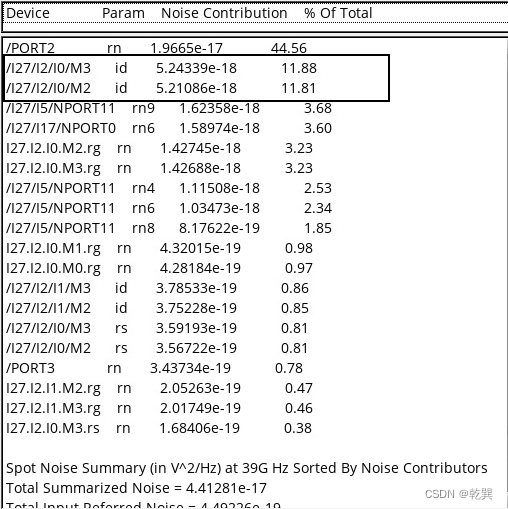

【Cadence】差分管噪声贡献差别很大的可能原因

举例:M2 M3是一对差分管,噪声贡献差别很大。 理想电感下二者贡献相同, 但在实际电磁仿真后,一个17.6%,一个5.6% 原因是: 电磁仿真存在交叉,不对称,中心抽头不是理想的交流地&#x…

于博士Cadence教程内容目录

最近花了一个多星期终于把于博士的60讲Cadence教程给看完了,虽然还是一头雾水,但是对用Cadence画原理图以及pcb的大致流程有了一个模糊的印象,后面的细节只要不停地百度就行了。这里把于博士视频的目录和大致内容列一下,不是很全&…

Allegro优化布线常用技巧

delete-cut

在排线布线过程中,有时候需要调整线序, 这时候,可以使用delete-cut,将需要调整的线, 首尾各剪断一小段线, 这样,中间部分,就变成了dummy net,就可以挂靠任意…

MOS管的特征频率ft

一、定义

特征频率是表征晶体管在高频时放大能力的一个基本参量

是指其电流放大系数下降到1时的频率;

二、计算方法

画出小信号模型 三、分析

因此增大过驱动电压,减小L可以增大ft。但随着垂直电场增强到一定程度,会导致迁移率明显逐渐减…

提示“ERROR #8003 More than one page is numbered 1.

可以通过双击原理图右下角 的title block,修改它的属性,主要是修改page count 和page number 即可。

Cadence OrCAD Capture TCL/TK脚本——DboGlobal

DboGlobalSymbol

DboGlobal_SetMirror

DboGlobal_GetPinType

DboGlobal_SetName

DboGlobal_GetGlobalSymbol

DboGlobal

DboGlobal_SetRotation

Cadence 仿真

电路的学习离不开仿真和实践,主流的仿真软件有很多,有用功pretues和mutisim,这次主要是工作中使用cadence,而且带有比较强大的仿真工具Pspice,所以选择了它 ,我使用的版本是cadence 17.4自带的。官方提供了…

硬件学习 软件Cadence day06 原理图网表导入PCB (过程和操作的错误),开始的画板

1.新建一个制作芯片的工程

1.打开 File ->New 2.填写信息,设置路径 2.原理图的网表导入

1.打开这个窗口

File -> import ->Logic.. 2.确定信息 3.解决网表导入时出现的错误

1. 第一个案列 (没有找到文件 也是这个)

比如说:

WARNING(…

Cadence OrCAD Capture 层次化电路设计展开的方法

🏡《总目录》 🏡《宝典目录》 🏡《上级目录》 目录1,概述2,展开方法3,总结B站关注“硬小二”浏览更多演示视频 1,概述 典型的层次化设计是指顶层模块中,调用1个电路模块超过…

Cadence :OrCAD命名优先级

由于AD支持Multiple Names,最近用OrCAD画原理图,犯了一个错误,记录如下:

OrCAD对于同一个网络,最终在网表中只有一个确定的名称,而在原理图中可能有各种不同的名称,包括自动生成的名称、Alias、…

2小时掌握Allegro PCB 封装焊盘设计专题

🏡《总目录》 🏡《宝典目录》 目录 1,概述2,大纲Cadence Allegro 通孔PAD制作方法Cadence Allegro 贴片PAD创建方法Cadence Allegro 异形焊盘制作之椭圆形通孔焊盘Cadence Allegro 热风焊盘的制作方法Cadence Allegro 向导创建DIP排针封装方法Cadence Allegro 向导创…

Concept HDL学习资料汇总

本篇博文目录:一.concept HDL相关概念知识1. Concept HDL2.Concept HDL与Cadence的区别3.Concept HDL与Cadence CIS之间的转换问题二.Cadence软件安装1.Cadence 16.6安装2.Cadence 17.x安装三.concept HDL视频学习资料四.concept HDL博文学习资料五.concept HDL书籍/文档资料一…

Cadence Allegro 导出Net loop Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Net loop Report作用3,Net loop Report示例3.1,Net Loop Summary3.2,Skipped Net Summary4,Net loop Report导出方法4.1,方法14.2,方法2

Cadence Allegro 导出Bill of Material Report详解

⏪《上一篇》 🏡《总目录》 ⏩《下一篇》 目录 1,概述2,Assigned Functions Report作用3,Assigned Functions Report示例4,Assigned Functions Report导出方法4.1,方法14.2,方法2B站关注“硬小二”浏览更多演示视频

linux建立软链接——以matlab为例

如果软件没有建立软连接,每次打开terminal就只是个黑黑的窗口,每次打开软件都要自己load一次,比较麻烦。 第一步:

在工作夹新建文档:project.cshrc 第二步:

在夹新建文档中写入:module laod m…

Cadence OrCAD Capture全局修改原理图的非本地库符号的方法图文教程Repalce Catch功能

⏪《上一篇》 🏡《总目录》 ⏩《下一篇》 目录 1,概述2,修改方法2.1,新建本地库2.2,待修改搬入本地库2.3,修改原理图符号2.4,全局更新原理图符号3,总结B站关注“硬小二”浏览更多演示视频 1,概述 在完成原理图设计

Cadence 16.6基本操作技巧

都是工作上碰到的需要学习的知识,比较实用。

1、修改Pin脚网络

set up --user preference Editor Logic--net logic Option处选择网络,然后find处选择Pins,之后点击要修改网络的Pin即可将原来的网络修改为所选择的网络。

2、在使用测量工具…

Cadence Allegro 导出Etch Detailed Length Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Etch Detailed Length Report作用3,Etch Detailed Length Report示例4,Etch Detailed Length Report导出方法4.1,方法1:4.2,方法2:B站关注“硬小二”浏览更多演示视频

cadence专题【1】--多引脚IC如何创建orcad原理图库

cadense下载说明新建工程一、采用传统方式创建1、新建库文件2、放置pin array3、修改管脚信息二、采用电子表格方式创建1、新建库文件2、Ctrlc、Ctrlvcadense下载说明

cadence是目前最流行的EDA,下载装机全交给阿狸狗即可。 浏览器搜索cadence吴川斌或点击链接: ht…

Cadence Allegro 导出Etch Length by Layer Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Etch Length by Layer Report作用3,Etch Length by Layer Report示例4,Etch Length by Layer Report导出方法4.2,方法14.2,方法2B站关注“硬小二”浏览更多演示视频

Cadence Allegro 导出Missing Fillets Report报告详解

⏪《上一篇》 🏡《上级目录》 ⏩《下一篇》 目录 1,概述2,Missing Fillets Report作用3,Missing Fillets Report示例3.1,PAD and Fillet parameters3.2,Missing Fillets4,Missing Fillets Report导出方法4.1,方法1:4.2,方法2:<

PCB,原理图 最流行的画图画板软件有哪些?

中国各行业领域流行的硬件工具情况

领域原理图 PCB图说明高端复杂产品(手机、电脑…)Cadence Concept + Cadence Allegro大公司使用,相对难上手中低端消费电子OrCAD Capture PADS Layout(PowerPCB)/ Rou…

![[原创]Cadence17.4,win64系统,构建CIS库](https://img-blog.csdnimg.cn/3800958cf6174a19bdec33d4576ba5ae.png)